Friday, November 22, 2013

Optimistic interpretation of Moore's Law Death

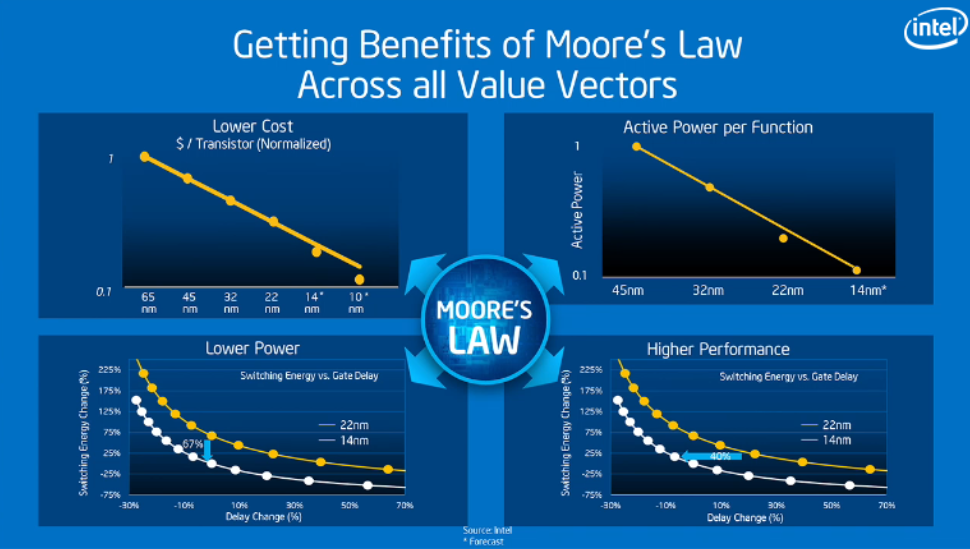

Intel is trying to convince us that progress i still here. Lower price per transistor ? But not taking in account drive to bigger wafers and better yield ! Than lower node at 14 nm. But something like that doesn't exist at all. Then, there are no advancements in low power and performance. 22 nm node can be somewhat optimized as it was previously, but not both at the same time and at the declared levels. And the last, but not the least lie: Active power is down. But what about leakage, when device is off ? It grows. Exponentially ! For all dark silicon INSIDE !

___________________________

99% BAD HARDWARE WEEK: UV projection sources at 133 nm interfere with SiO2 on wafer bandgap. Thus, industry forced to extend use of 193nm deep UV photolithography

___________________________

99% BAD HARDWARE WEEK: UV projection sources at 133 nm interfere with SiO2 on wafer bandgap. Thus, industry forced to extend use of 193nm deep UV photolithography