Saturday, June 17, 2006

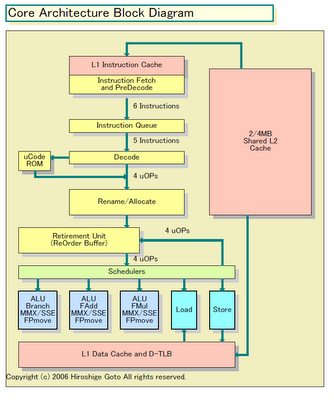

Intel's versus AMD's microarchitecture

| L1 Cache | Instructions - 32KB Data - 32KB | Instructions - 64KB Data - 64KB |

| L1 Cache Latency | 3 Cycles | 3 Cycles |

| L1 Associativity | 8-way | 2-way |

| L1 TLB | Instructions - 128 Entries Data - 256 Entries | Instructions - 32 Entries Data - 32 Entries |

| L2 Cache | Max 4MB | Max 1MB |

| L2 Cache Latency | 12 Cycles | 12-14 Cycles |

| L2 Associativity | 16 Way | 16 Way |

| L2 Bandwidth | 256Bit | 128Bit |

| L2 TLB | n/a | 512 Entries |

| Memory Controller | External | Internal |

| Pipeline Stage | 14 | 12 |

| Branch Predictor Bandwitdh | 20Bytes | 16Bytes |

| Decode to Execute Unit | 3 Simple + 1 Complex | 3 Complex |

| FPU | 1FMUL + and 1 FADD + 1 FStore + 1 FLoad | 1FMUL + and 1 FADD + 1 FStore |

| Integer Unit | 3 Int + 2 AGU | 3 Int + 3 AGU |

| Load/Store | 1 Load + 1 Store | 1 Load & Store |

| ALU | 3 | 3 |

| SSE Unit | 3 - 128Bit | 2 - 64Bit |

FP Unit | 2 | 2 |

64 bit microarchitecture differences in addition. So much about Intel's "new" microarchitecture advantage over AMD's old proven one.

This post link