Tuesday, October 10, 2006

IBM clock hits 4-5 Ghz by mid 2007

Actually, IBM's SOI will reach some 4,4GHz clock . IBM is now in a systems test and debug phase using the Power6. The CPU will run at speeds between 4-5GHz with a total of 8Mbytes L2 cache and a 75Gbyte/second link to external memory. In addition, IBM will link its Power CPU for the first time to an external embedded controller.The chip can be fully operated at as little as 0.8V.

Interestingly enough , about the same time, AMD's 65nm SOI will start with K8L race towards 3,5Ghz so AMD has kept 3 issues per clock architecture. Intel? Where are you Intel?

Actually, Intel is here.

It is interesting to note that IBM is ramping up frequency for their next generation 65nm Power6 design to over 4GHz in mid 2007 which is what Intel is trying to achieve as well for their 45nm Penryn since it will still take a while for Octo-core to be available.

So, what is the trouble? Well the link quite recently has been sponsored by ... Intel. Do you feel, they are a bit biased?

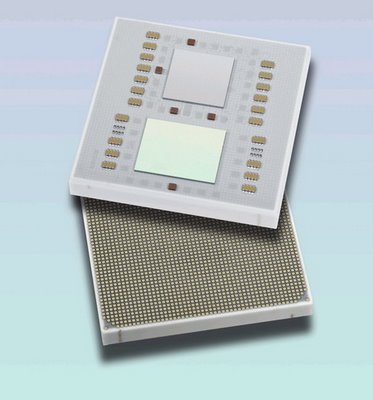

I think it is highly unlikely that IBM will try to push clock speeds to 6 GHz as the initial Power6 specs suggested a number of years ago. Rather than do this, I think IBM will probably have brought more electronics onto the Power6 core to boost performance and clock will not rise more than 4,4Ghz. If L3 caches are not shrunk and then integrated on the chip with the Power5+, you can bet IBM might do it with the Power6, and then possibly add an external L4 cache to keep those hungry processors fed. So the second die on this Power6 module is L4? Or, still separate 32 MB L3 similar to Power 5+ processor? Probably something in between, at least for dual core packages:

I think it is highly unlikely that IBM will try to push clock speeds to 6 GHz as the initial Power6 specs suggested a number of years ago. Rather than do this, I think IBM will probably have brought more electronics onto the Power6 core to boost performance and clock will not rise more than 4,4Ghz. If L3 caches are not shrunk and then integrated on the chip with the Power5+, you can bet IBM might do it with the Power6, and then possibly add an external L4 cache to keep those hungry processors fed. So the second die on this Power6 module is L4? Or, still separate 32 MB L3 similar to Power 5+ processor? Probably something in between, at least for dual core packages:2x4MB large L2 and 32MB L3 on package module.

The only objection of mine is that Power 6 will probably support in a real world insufficient 200 simultaneous operation systems, of 1024 possible. : )